软件介绍

系统运行环境/版本:官方特别版

maxplus2可编程逻辑设计软件平台 官方特别版软件截图

maxplus2可编程逻辑设计软件平台 官方特别版介绍

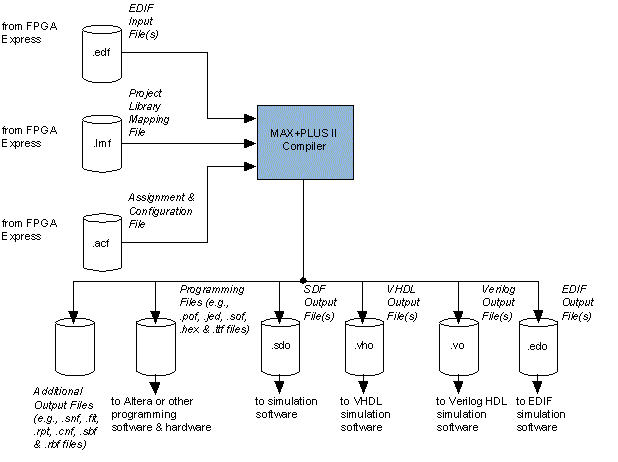

MAX+plus II 是最新版是美国Altera公司开发的大型可编程逻辑设计软件平台

功能:

它支持Altera公司不同结构的可编程逻辑器件,能满足用户各种各样的设计需要。MAX+plus II具有突出的灵活性与高效性,为设计者提供了多种可自由选择的设计方法和工具。

MAX+PLUSII 普遍认为MaxplusII曾经是最优秀的PLD开发平台之一,适合开发中小规模PLD/FPGA。

在这里我们可以先看一看用FPGA/CPLD开发工具进行电路设计的一般流程,通常可将FPGA/CPLD设计流程归纳为以下7个步骤,这与ASIC设计有相似之处。

流程:

1.设计输入。在传统设计中,设计人员是应用传统的原理图输入方法来开始设计的。自90年代初, Verilog、VHDL、AHDL等硬件描述语言的输入方法在大规模设计中得到了广泛应用。

2.前仿真(功能仿真)。设计的电路必须在布局布线前验证电路功能是否有效。(ASCI设计中,这一步骤称为第一次Sign-off)PLD设计中,有时跳过这一步。

3.设计编译。设计输入之后就有一个从高层次系统行为设计向门级逻辑电路设转化翻译过程,即把设计输入的某种或某几种数据格式(网表)转化为软件可识别的某种数据格式(网表)。

4.优化。对于上述综合生成的网表,根据布尔方程功能等效的原则,用更小更快的综合结果代替一些复杂的单元,并与指定的库映射生成新的网表,这是减小电路规模的一条必由之路。

5.布局布线。在PLD设计中,3-5步可以用PLD厂家提供的开发软件(如 Maxplus2)自动一次完成。

6.后仿真(时序仿真)需要利用在布局布线中获得的精确参数再次验证电路的时序。(ASCI设计中,这一步骤称为第二次Sign—off)。

7.生产。布线和后仿真完成之后,就可以开始ASCI或PLD芯片的投产

ALTERA的MAX+plus II开发环境安装说明:

1. 运行"PCALTERA32BIT"目录下的"SETUP.EXE",

点击Install SoftwareMAX+PLUS II BASELINE Software安装软件。

Next按钮完成安装。

2. 第一次运行MAX+plus II时,会弹出一个"遵守协议"对话框,

用鼠标将内容下拉到最后, 选择“OK“。

3. 将安装盘目录下的******授权文件,复制到MAX+plus II的安装目录下(如"C:MAXPLUS2"目录)。

4. 再次启动MAX+plus II,选择菜单[Option]->[****** Setup]功能,

在弹出的对话框中,按"Browse"按钮,选择刚才复制的授权文件,

确认退出,退出MAX+plus II开发环境,再次运行MAX+plus II即可。

5. 打开控制面板,打开添加/删除硬件: